International Journal of Scientific Research in Computer Science, Engineering and Information Technology © 2019 IJSRCSEIT | Volume 5 | Issue 4 | ISSN : 2456-3307 DOI : 10.32628/CSEIT11953129

## Network Security - A Literature Review

Dr. Indira Reddy, A. Srilekha

Department of Information Technology, Sreenidhi Institute of Science and Technology, Hyderabad, Telangana,

India

### ABSTRACT

Advanced Encryption Standard algorithm also known as Rijndael calculation is a sort of Network Security calculation which is for the most part utilized in a wide range of wired and remote computerized correspondence systems between two end users for Secure transmission of data especially over a public network. In this work we dissect the structure and plan of new AES, following three criteria: a) opposition against every single known assault; b) speed and code conservativeness on a wide scope of stages; and c) structure effortlessness. The use of Internet has grown fast currently for commercial transactions and has huge demand for privacy of the data and security for the networks. The Synthesis Tool was set to enhance Speed and Power. The region and throughput are cautiously exchanging off to make it appropriate for remote military correspondence and versatile communication.

**Keywords:** Cryptography, Advanced Encryption Standard (AES), Encryption, Unscrambling,Rijndael, Hardware Description Language (HDL), Field Programmable Gate Cluster (FPGA).

#### I. INTRODUCTION

In computerized systems, information security is accomplished by Cryptography. It includes different strategies for building up a protected and secure correspondence connect in nearness of foes. Cryptographic calculations mean to give obstruction against secret word assaults, spying and hacking. Numerous kinds of cryptographic calculations are in presence.

In 2001, The National Institute of Standards and Technology (NIST) have institutionalized AES Encryption and Decryption Algorithm which transformed into Federal Information Processing Standard (FIPS-197). This calculation was created by two expert cryptographers Joan Daemen and Vincent Rijmen. It discovers applications in Mobile Phones, Smart Cards, Magnetism Cards, Intel Core Processors Family, Automated Teller Machines (ATM), different other transmission conventions institutionalized by IEEE, IEEE 802.11i WPA2 standard Wi-Fi systems for secure encryption and advanced video frameworks, and so on., guaranteeing wellbeing, security and unwavering quality of information transmission.

Due to less key size in DES having less security levels we are going for Advanced Encryption Standard (AES).

Rijndael, a variation to the Square block cipher due to the same creators , isn't a Feistel figure like DES. As it is outstanding, in DES and other Feistel figures, in each cycle one portion of the square is exposed to a capacity which includes subkey material, which should be non- direct and which may not be (and, truth be told, isn't in DES) invertible. In any case, the round in general is ensured to be invertible since the half of the square exposed to that work isn't changed. Rather, the other portion of the square is changed, by being exposed to a XOR operation with the yield of that work. In this manner, a round is its very own converse, and unscrambling is equivalent to encryption, then again, actually the subkeys are utilized backward request. As opposed to DES, and other square figures, the round transformation of Rijndael does not have the Feistel structure. Rather, the round change is com- presented of three particular invertible uniform transformations, called layers.

The particular decisions for the extraordinary layers are for a substantial part dependent on the use of the Wide Trail Strategy, a structure technique to give resistance against direct and differential cryptanalysis.

## II. LITERATURE REVIEW

BanraplangJyrwa and Roy Paily [1]The enhanced code for the Rijndael calculation with 128 piece keys has been created strategies, for example, cryptography, steganography, water veiling and scrambling have been created to keep source. It tends to structure, equipment execution and execution testing of AES calculation.

Hoang Trang[2]:A Proposed FPGA based execution of the Advanced Encryption Standard.This gives low unpredictability engineering and effectively accomplishes low dormancy just as high throughput. simulation results, execution results are given and thought about past detailed structures.

JalelRajeb[3] This paper exhibits a rundown of our work to structure a proficient usage of Rijndaelalgorithm, it is the new Advanced Encryption Standard received by NIST and two distinctive equipment executions are displayed and investigated.

P.Kitsos, N.Sklavos[4] A start to finish security design and its VLSI execution for the GPRS is proposed in this paper. The security offered by GPRS is like that offered by the Global Mobile System(GSM).

Abhijith.P.S, Mallika Srivastava, AparnaMishra[5] There are numerous engineering recommendations for AES Rijndael calculation, however a considerable lot of them are poor as far as territory what's more, speed. This paper proposes an alternate way to deal with increment speed by using lesser assets accessible in FPGA.

Muhammad FarhanWali, Muhammad Rehan[6] This paper talks about the powerful coding of Rijndael calculation, Advanced Encryption Standard (AES) in Hardware Description Language, Verilog. The paper gives basis of every single change done in the calculation.

C. Sanchez-Avilaf and R. Sanchez-Reillot[7] In this work we investigate the structure and plan of new AES, following three criteria: an) opposition against every single known assault; b) speed and code minimization on a wide scope of stages; and c) structure straight forwardness; also as its likenesses and dissimilarities with other symmetric figures.

N.Sivasankari[8] The Propelled Encryption Standard is the most generally utilized Symmetric figure today. The calculation utilizes a mix of Selective OR activities (XOR), octet substitution with a S-box, line and section turns, and a Mix Column. An balanced designing for AES with redesigned key advancement and for the Mix Column/Inverse Mix Column activities are fixed to diminish the chip district.

Prachi V. Bhalerao[9]In this paper we show that how an adjusted structure in these Equipment gadgets results in huge improvement of the structure productivity. The regular plan of AES is defenseless for cryptanalysis. B.NageswaraRao[10] In our task, we increment the number of rounds (Nr) to 16 for the encryption and decoding procedure of AES calculation, which results in additional security to the framework. Exploratory outcomes and Theoretical examination demonstrated that this AES strategy give fast just as less exchange of information over the unbound channels.

ArturGielata[11] In this paper we examine equipment implementation of AES-128 figure standard on FPGA innovation. In numerous organize applications programming executions of cryptographic calculations are moderate and wasteful. To take care of that issues custom design in reconfigurable equipment was proposed to accelerate the execution and adaptability of Rijndael calculation execution.

Ahmed[12] Developing necessities for fast, high volume secure correspondences joined with physical security, equipment usage of cryptography happens. A FPGA usage is a halfway arrangement between broadly useful processors (GPPs) and application explicit coordinated circuits (ASICs).

Mr.Atul [13] Our structure for AES 128-piece encryption/decoding calculation was orchestrated, executed by Altera instruments. Table condenses the equipment assets required by fundamental building squares and gives itemized correlations with the other plans.

K.Järvinen[14] From the investigations exhibited above, FPGAs are considered one of the significant equipment stages and basic part for the cryptographic calculations execution. FPGAs offer a lot simpler and sensibly modest answer for the execution of cryptographic calculation.

D. S. Kundi[15] For implanted applications, the attention is on the decrease of territory rather than the throughput. Consequently, a few usage with little rationale prerequisites have likewise been distributed.

A. Aziz[16] SubBytes change is actualized utilizing S-Box, which is profoundly computationally concentrated and devours over 75% of FPGA assets.

A. H. Saleh[17] Introduced a smaller execution of AES encryption and decoding with all key lengths utilizing a novel State portrayal, which takes care of the issue of getting to the two lines and segments of the State.

N. Pramstaller[18] The proposed design was actualized in Spartan-3 XC3S400-5 chip with region use of 2699 cuts and accomplishing a throughput of 10 Mbps. Pramstalleretc al.

## **III. AES ENCRYPTION AND DECRYPTION**

The AES calculation is symmetric, square figure and iterative sort in nature. It is symmetric since it utilizes a similar key for both encryption and unscrambling forms. It is a square figure since it forms singular information squares having fixed length of 128 bits with a figure key having variable key lengths picked freely as 128, 192 or 256 bits. Subsequently, this calculation can be utilized with three diverse key lengths which results in three particular configurations alluded to as AES-128, AES-192 and AES-256. It is iterative in light of the fact that the means associated with this calculation are rehashed various occasions. These emphasess are likewise called as rounds. The absolute number of cycles or adjusts in Encryption and Decryption procedures relies upon the measure of the key used. The 128-piece information square is assembled into 16 bytes and correspondingly mapped into a variety of size 4 X 4 called as the State.

In AES there are 3-Formats AES-128, AES-192, AES-256 defines the key lengths of the formats. In these Formats number of Rounds of the operation also changes. In AES-128 Format there are 10 Rounds of Operation. Similarly, For AES-192 Format there is 12 Rounds of Operation and in AES-256 Format there is 14 Rounds of Operation.

| AES     | Key      | Plain    | No.of  |

|---------|----------|----------|--------|

|         | Length   | Text     | Rounds |

| AES-128 | 128 bits | 128 bits | 10     |

| AES-192 | 192 bits | 128 bits | 12     |

| AES-256 | 256 bits | 128 bits | 14     |

# **TABLE I.** CONNECTION BETWEEN KEY LENGTHAND TOTAL NUMBER.

## **BLOCK DIAGRAM**

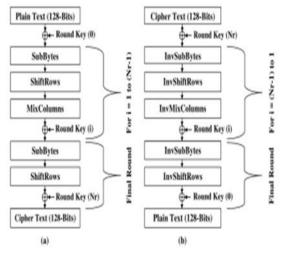

Fig 2. AES ENCRYPTION AND DECRYPTION

Figure demonstrates the schematic square chart of AES Encryption and Decryption squares. Every one of them fuses four changes (Sub Bytes, Shift Rows, Mixed Columns and AddRoundKey) in each round. Be that as it may, in the last round, the Mixed Columns change is disregarded.

**Pre Round Operation:** In Pre Round Operation, Exor Operation is performed between Key and Plain Text. The obtained 128 bit output is given to sub Byte module. Pre Round Operation is used only in first round and is very important step in this algorithm.

Sub Byte step: The traditional way of explaining the byte substitution step that involves using a  $16 \times 16$  lookup table.In the SubBytes step, each byte in the

state is replaced with its entry in a fixed 8-bit lookup table (LUT).In the SubBytes step, each byte in the *state* matrix is replaced with a SubByte using an 8-bit substitution box(LUT), the Rijndael S-box. This operation provides the non-linearity in the cipher. The S-box used is derived from the multiplicative inverse over GF(28), known to have good nonlinearity properties.

The ShiftRows step: In the Shift Rows step, bytes in each row of the state are shifted cyclically to the left. The number of places each byte is shifted differs for each row. The Shift Rows step operates on the rows of the state; it cyclically shifts the bytes in each row by a certain offset. For AES, the first row is left unchanged. Each byte of the second row is shifted one to the left. Similarly, the third and fourth rows are shifted by offsets of two and three respectively. For blocks of sizes 128 bits and 192 bits, the shifting pattern is the same. Row is shifted left circular by bytes.

**The Key Expansion:**The principle key is extended so as to look after security. Key Expansion is accomplished for each round by increasing with various key constants determined for various rounds. Key development yield is furthur given to Add round Key as indicated in the AES calculation.

In this Key Expansion process we will utilize LUT's with the goal that the duplication is made basic. The function Key Expansion() merely supplies a much extended (and changed) key for use by the Add RoundKey() function in the fundamental AES calculation. This completes a byte-wise restrictive or of 4\*Nb = 16 bytes during an era of the key with the 4\*Nb = 16 bytes of the state. Progressive sections of 4\*Nb = 16 bytes of the extended key are selective ored in before the rounds of the calculation, amid each round, and toward the finish of the rounds. At last, there are Nr rounds, but Nr+1 exclusive- ors of parts of the extended key. Since none of the extended key is utilized more than once, this implies that calculation needs 4\*Nb\*(Nr+1) = 16\*(Nr+1) bytes of

extended key, and this is only the sum given by the Key Expansion() function.

## IV. LUTS USED FOR IMPLEMENTATION OF AES ON FPGA

The LUT based implementation of AES algorithm on FPGA is a traditional approach. It is very simple and easy to implement the desired functionality. When it is synthesized, it considerably occupies a less amount of area on FPGA. So for this purpose, the following LUTs are used. Show LUTs for actualizing Sub Bytes and Inv Sub Bytes changes individually. show LUTs for getting the results of GF (28) duplications engaged with (1) and (2) of Mixed Columns and Inv Mixed Columns changes individually.

#### V. CONCLUSION

The target of this paper was to show the equipment execution of Advanced Encryption Standard (AES) calculation. The mix of security, and rapid execution and territory settles on it an awesome decision for remote system. This ponder presents math forms appropriate for equipment amid encryption and decryption. The LUT based arrangement approach gives less confounding plan and extras the taking care of time, as it were, by recovering the important qualities from memory areas. Bringing esteems from memory areas is commonly quicker than executing complex calculation activities. The generalproposed configuration is observed to have great effectiveness as far as different execution measurements like inertness, throughput, speed/deferral, region and power.

#### **VI. REFERENCES**

- [1]. Banraplang Jyrwa and Roy Paily ,ECE dept ,NIT Jalandhar and IIT Guwahati, IEEE.

- [2]. Hoang Trang, Nguyen Van Loi University of Technology, IC Design Research & amp;

Education center, VietNam National University HochiMinh City.

- [3]. Jalel Rejeb, Vidyashankar Ramaswamy Electrical Engineering Department, san Jose State University.

- [4]. P.Kitsos, N. Sklavos and O. Koufopavlou University of Patras/Electrical and Computer Engineering Department, Patras.

- [5]. Abhijith.P.S, Mallika Srivastava, Aparna Mishra, Dept. of Microelectronics, IIITA Indian Institute of Information Technology, Allahabad, India.

- [6]. Muhammad Farhan Wali, Muhammad Rehan Division of Electronics Engineer,NED University of Engineering and Technology, Karachi.

- [7]. C. Sanchez-Avilaf and R. Sanchez-Reillot Dpto. de Matematica Aplicada, E.T.S.I. Telecomunicacion, Universidad Politecnica de Madrid, 28040 Madrid.

- [8]. N Sivasankari, K Rampriya1 and A Muthukumar Department of ECE, Mepco Schlenk Engineering College, Sivakasi, India.

- [9]. Prachi V. Bhalerao, Rahul D. Ghongade2 , Vishal B. Langote ExTC Department and SGBAU University, India H.O.D., ExTC Department and SGBAU University, India.

- [10]. B. Nageswara Rao1 , D. Tejaswi, K. Amrutha Varshini3 , K.Phani Shankar, B. Prasanth International Journal For Technological Research In Engineering Volume 4, Issue 8, April-2017.

- [11]. William Stallings, "Cryptography and Network Security-Principles and Practice,"Fifth Edition, Prentice Hall, Pearson.

- [12]. Ahmad, N.; Hasan, R.; Jubadi, W.M Plan of AES S-Box utilizing combinational rationale improvement, IEEE Symposiumon Industrial Hardware and Applications (ISIEA), pp. 696-699, 2010.

- [13]. Mr. Atul M. Borkar, Dr. R. V.Kshirsagar and Mrs. M. V. Vyawahare, FPGA Implementation

of AES International Conference on Electronics Computer Technology (ICECT), pp. 401-405, 2011 third.

- [14]. K. Järvinen, M. Tommiska, and J.Skyttä, Near study of superior cryptographic calculation usage on FPGAs, in Proc. of IEE on Data Security, Vol. 152,pp. 3-12, 2005.

- [15]. D. S. Kundi, S. Zaka, Q. Ain and A.Aziz,A minimized AES encryption center on Xilinx FPGA", in Proc. of second Worldwide Conference on Computer, Control and Correspondence, pp.1-4, 2009.

- [16]. A. Aziz and N. Ikram, Memory effective usage of AES S-boxes on FPGA& Journal of Circuits, Systems, and PCs.

- [17]. A. H. Saleh and S. S. B Ahmed,Elite AES configuration utilizing pipelining structure over GF ((24) 2), in Proc. Of IEEE International Conference on Signal Processing and Correspondences, pp. 716-, 2007.

- [18]. N. Pramstaller and J. Wolkerstorfer, An all inclusive and productive AES co-processor for field programmable rationale clusters, in Proc. of fourteenth International Conference on Field- Programmable Logic and its Applications, pp. 565-574, 2004.

- [19]. FIPS-197, NIST National Institute of Standards and Technology, "Announcing the ADVANCED ENCRYPTION STANDARD (AES),"

- [20]. W. Wei, C. Jie and X. Fei, "An Implementation of AES Algorithm on FPGA," IEEE 9th Int. Conf. on Fuzzy Systems and Knowledge discover 2012.

- [21]. U. Kretzschmar, A. Astarloa, J. Lazaro, U.Bidarte and J.Jimenez, "Robustness analysis of different AES implementations on SRAM based FPGAs,.

- [22]. J. Daeme and V. Rijmen, "AES proposal: Rijndael," NIST AES Proposal, June 1998.

- [23]. W. Stallings, "Cryptography and network security principles and practice," Pearson edition 2009, pp. 135-160.

- [24]. P.V.S. Shastry, A. Agnihotri, D. Kachhwaha, J. Singh and M.S. Sutaone, "A Combinational Logic Implementation of S-Box of AES," IEEE 54 th Int. Midwest Symp. on Circuits and Systems (MWSCAS), Aug.2011.

- [25]. S. Kaur and R. Vig, "Efficient Implementation of AES Algorithm in FPGA Device,"

- [26]. H. Trang and N.V. Loi, "An efficient FPGA implementation of the Advanced Encryption Standard algorithm," IEEE Int.

- [27]. N. Koblitz, A Course in Number Theory and Cryptography, Springer-Verlag New York Inc., 1987.

- [28]. M. Matsui, Linear Cryptanalysis method for DES cipher, Advances in Cryptology, Proc. Euro- crypt'93, LNCS 765, Springer-Verlag, 1994, pp. 386-397.

- [29]. S. Murphy and M. Robshaw, New observations on Rijndael, version of August 7, 2000.

- [30]. B. Schneier and D. Whiting, APerformance Comparison of the Five AES Finalist, 15 March 2000.

- [31]. J. Daemen, Cipher and hash function design strategies based on linear and differential cryptanalysis,Doctoral Dissertation, March 1995, K.U. Leuven.

- [32]. M. Hellman and S. Langford, Differential-Linear Cryptanalysis, Advances in Cryptology, Proc.Cryto'94, LNCS-839, Springer-Verlag, 1994.

#### Cite this article as :

Dr. Indira Reddy, A. Srilekha, "Network Security - A Literature Review", International Journal of Scientific Research in Computer Science, Engineering and Information Technology (IJSRCSEIT), ISSN : 2456-3307, Volume 5 Issue 4, pp. 50-55, July-August 2019. Journal URL : http://ijsrcseit.com/CSEIT11953129